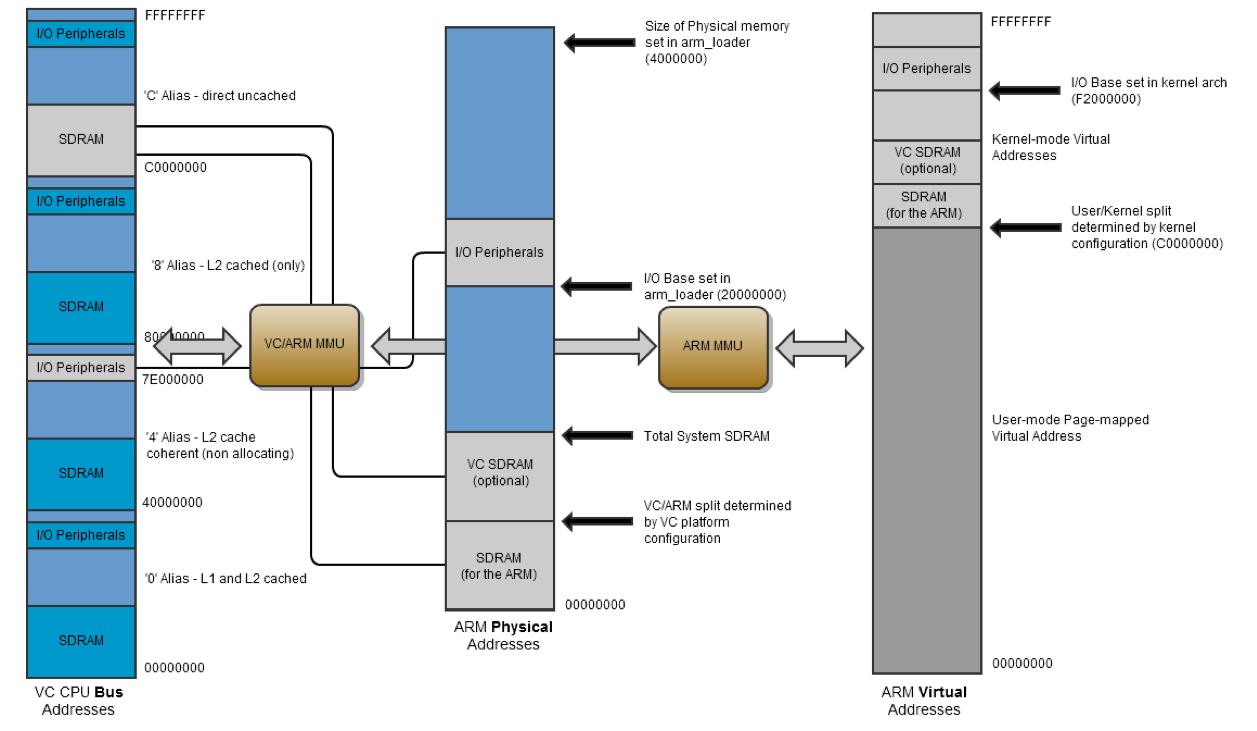

Now time to have a look at memory model. The BCM2835 gives next picture:

Actually when U-Boot pass the control, we have memory model equal to just physical addresses (middle column), so we just do not do anything we can perfectly sit with memory model equal with physical.

So then, our kernel is loaded at 0x8000, which is 32KB, and we are going to use the low 0-0x8000 memory part for kernel structures and kernel stack (which is not expected to be too much)

Now back to loader, we need to do some specific arm things before passing control: first we need to disable interrupts:

1MOVW $(PsrDirq|PsrDfiq|PsrMsvc), R1 /* SVC mode: interrupts disabled */

2MOVW R1, CPSR

Set address for stack: we decided to put Mach structure at address 0x2000 (8KB), so let’s have a stack at MACHADDR+BY2PG (added a page 4KB) = 12KB, as result we will have stack area for kernel as 0x3000-0x8000 (12KB–32KB). It is 20KB, which is expected as enough of all kernel routines.

1MOVW $(MACHADDR+BY2PG-4),SP /* stack; 4 bytes for link */

Enable cycle counter:

1MOVW $1, R1

2MCR CpSC, 0, R1, C(CpSPM), C(CpSPMperf), CpSPMctl

Enable caches:

1MRC CpSC, 0, R0, C(CpCONTROL), C(0), CpMainctl

2ORR $(CpChv|CpCdcache|CpCicache), R0

3MCR CpSC, 0, R0, C(CpCONTROL), C(0), CpMainctl

4MOVW $0, R0

5MCR CpSC, 0, R0, C(CpCACHE), C(CpCACHEinvi), CpCACHEwait

(these codes I took from 9pi, so may not good explain step-by-step, I would appreciate if pointed to much better description of all specifics).

Resulting load.s:

1#include "mem.h"

2#include "armv6.h"

3

4TEXT _start(SB), 1, $-4

5 MOVW $setR12(SB), R12 /* static base (SB) */

6 MOVW $(PsrDirq|PsrDfiq|PsrMsvc), R1 /* SVC: interrupts disabled */

7 MOVW R1, CPSR

8

9 MOVW $(MACHADDR+BY2PG-4),SP /* stack; 4 bytes for link */

10

11 MOVW $1, R1

12 MCR CpSC, 0, R1, C(CpSPM), C(CpSPMperf), CpSPMctl /* counter */

13

14 MRC CpSC, 0, R0, C(CpCONTROL), C(0), CpMainctl /* caches */

15 ORR $(CpChv|CpCdcache|CpCicache), R0

16 MCR CpSC, 0, R0, C(CpCONTROL), C(0), CpMainctl

17 ISB

18

19 BL ,main(SB)

File armv6.h with all needed constants I took from 9pi sources.

FILES: